RESEARCH

自動運転やChat GPT。深層学習や生成AI技術は日常生活を一新し、豊かな暮らしを実現しつつあります。

AI技術の課題は消費電力です。大量のデータに対して膨大な積和演算を行う必要があり、多くの電力を消費します。

AI処理を行うサーバーの消費電力は指数関数的に増大しています。

電力危機の解決には、従来の延長線上にないAI時代に特化した次世代集積回路(Beyond IC)が必要です。

私たちはAI処理に特化した布線論理型プロセッサや3次元集積技術を研究、3桁以上の低電力化を実現します。

持続可能で発展的で、AIをあらゆるところに活用した豊かな社会の実現に貢献します。

THEME 01AIプロセッサ

現在のAI技術は大脳の神経回路を模倣して生まれた、ニューラルネットワーク技術がベースとなっています。

ニューロンと呼ばれる素子が多数のシナプスと呼ばれる神経網を介して信号伝送を行うことを模倣し、非常に巨大でスパースな疎行列の積和演算を膨大な回数繰り返し行います。行列計算が得意なGPUを活用することで低電力化が実現されていますが、計算の途中結果や学習結果を記憶するメモリとの通信が新たな課題となっています。

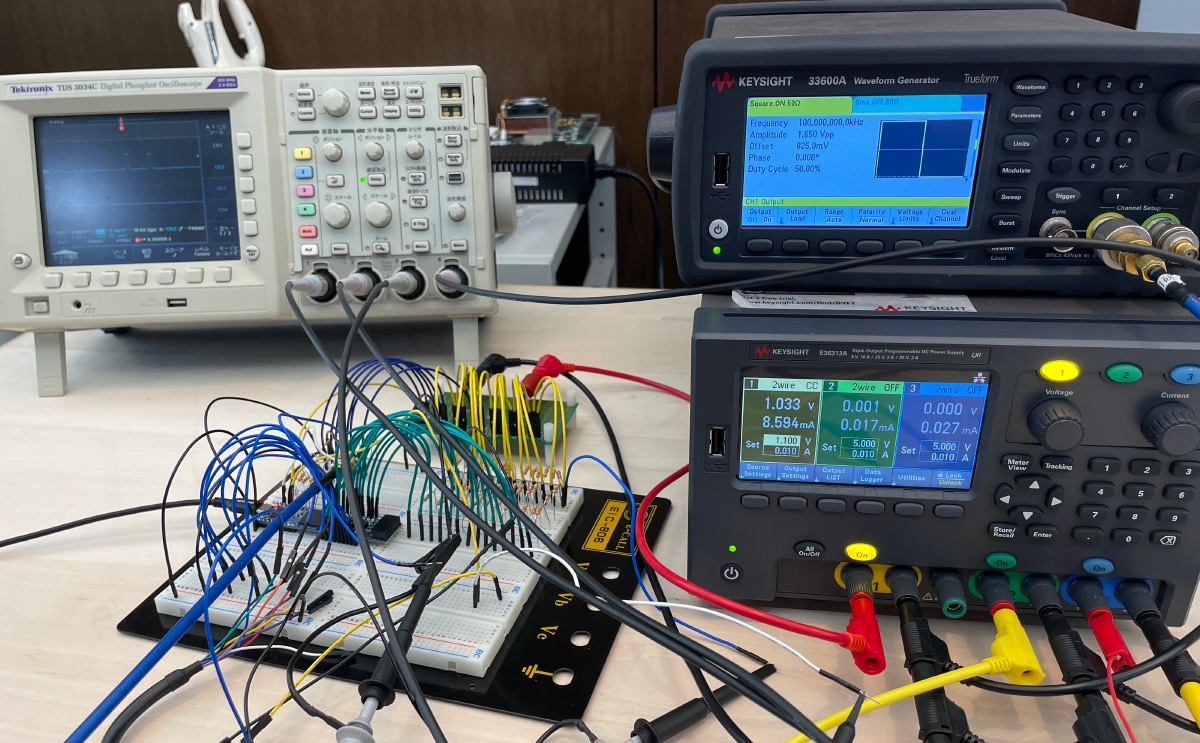

私たちは半導体集積回路そのものだけでなく、実装するニューラルネットワークモデルにも着目。ニューラルネットワーク×半導体回路の協調設計(Co-Design)により、高電力効率なAIプロセッサを研究開発しています。

MITや東大の神経科学の研究者と議論しながら、大脳の特徴を真似”Neuro-inspired”な低電力AIプロセッサを開発します。従来よりも1/1000の低電力化を実現し、インプランタブルなAIプロセッサの実現を目指します。

最近の研究成果:

[1] A. Kosuge, Y. C. Hsu, R. Sumikawa,T. Ishikawa, M. Hamada, and T. Kuroda, "A 10.7-μJ/frame 88% Accuracy CIFAR-10 Single-chip Neuromorphic FPGA Processor Featuring Various Nonlinear Functions of Dendrites in Human Cerebrum," in IEEE Micro, vol. 43, no. 6, pp. 19-27, Nov.-Dec. 2023.

[2] A. Kosuge, R. Sumikawa, Y. -C. Hsu, K. Shiba, M. Hamada, T. Kuroda, "A 183.4nJ/inference 152.8uW Single-Chip Fully Synthesizable Wired-Logic DNN Processor for Always-On 35 Voice Commands Recognition Application," in IEEE Symposium on VLSI Circuits, June 2023.

[3] D. Li et al., "Efficient FPGA Resource Utilization in Wired-Logic Processors Using Coarse and Fine Segmentation of LUTs for Non-Linear Functions," in IEEE International Symposium on Circuits and Systems (ISCAS), May, 2024 (To be presented).

最近の報道:

MIT Technology Review Japan : 35歳未満の発明家

https://www.technologyreview.jp/l/innovators_jp/261818/Atsutake-Kosuge/

THEME 023次元集積

Chat GPTや生成AI技術は、極めて膨大なデータを用いて開発されており、YouTubeやInternet上に広がる無数の知識を学習により獲得しています。大脳の神経回路網と同じく、ニューロン間をつなぐシナプスの重み係数として、知識がニューラルネットワーク内に蓄積されます。こうして得られた重み係数の容量は数テラバイトにも及びます。

現在の半導体技術では1台のプロセッサで処理することはできず、数百台のプロセッサを連結させたスーパーコンピュータが必要です。プロセッサの数が増えるにつれ、プロセッサ間の通信距離が延び消費電力も急増します。

AIの規模は大きいほど性能が良いことが知られているため、今後も指数関数的にメモリ量は増え、電力も急増するとみられています。

AIを保存するメモリや、大量の計算を行うプロセッサ、これらは全て半導体集積回路で構成されています。この半導体集積回路はトランジスタと呼ばれる素子で構成され、2年ごとに微細化が進み、メモリ容量は格段に増えプロセッサの性能は向上してきました。しかし、このトランジスタの微細加工技術は原子のサイズに近づき、もはやこれ以上の微細化は困難といった状況に達しつつあります。微細化に依らずに規模を拡大するための、新たな集積回路方式が必要です。

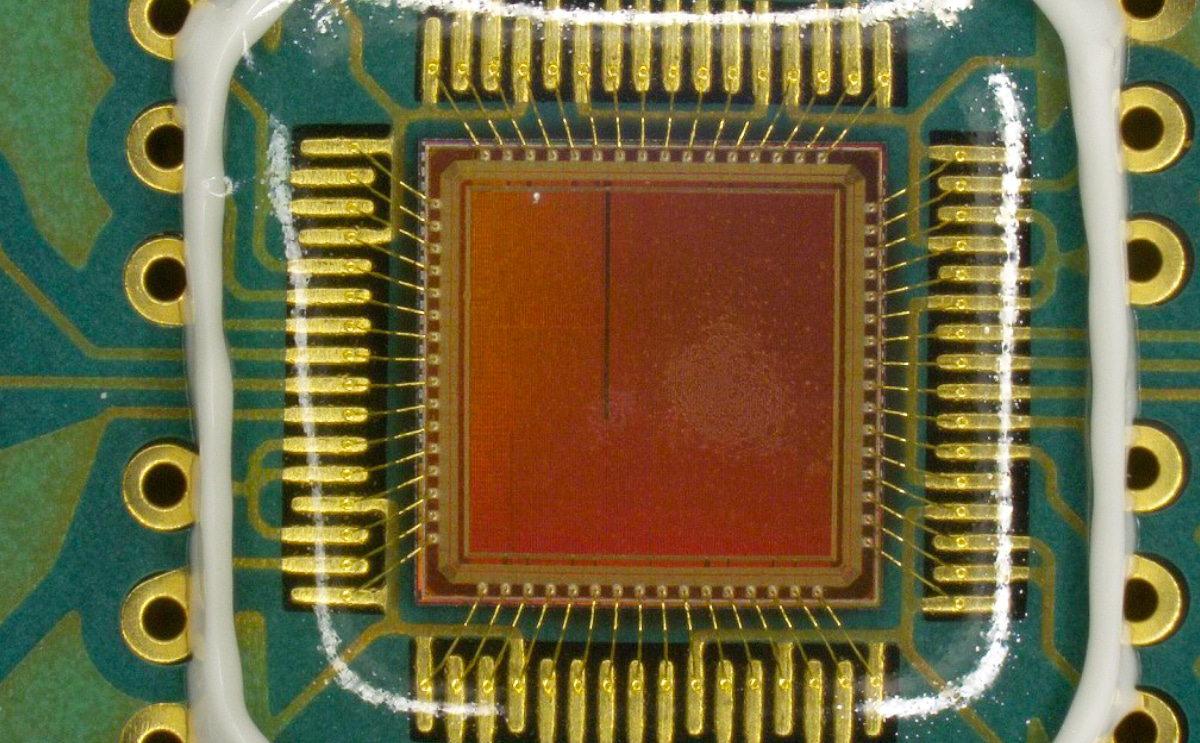

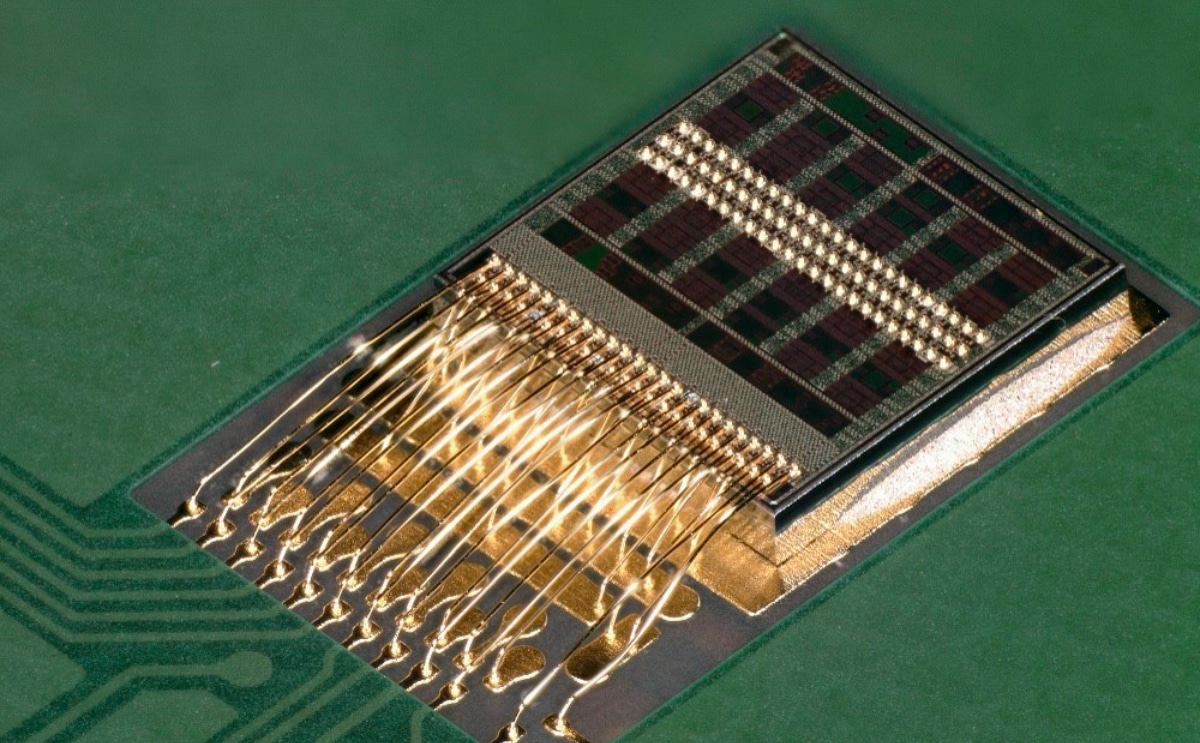

私たちは3次元集積回路技術を研究します。複数のメモリチップやプロセッサチップを重ねたキューブを構成します。このキューブに、高密度かつ低電力な信号配線を大量に実装し、1つのキューブだけで高度なAI処理を実現します。

これまで複数のスパコンを必要としていたAIモデルを手のひらサイズで実現し、電力消費を抑えます。さらに物理的にどこでも制約なく実装できるようになり、自動車やロボットに高度な知性を宿すことが可能になると考えています。

最近の研究成果:

[1] K. Shiba, M. Okada, A. Kosuge, M. Hamada and T. Kuroda, "A 12.8-Gb/s 0.5-pJ/b Encoding-less Inductive Coupling Interface Achieving 111-GB/s/W 3D-Stacked SRAM in 7-nm FinFET," in IEEE Solid-State Circuits Letters, vol. 6, pp. 65-68, March 2023.

[2] K. Shiba, M. Okada, A. Kosuge, M. Hamada, and T. Kuroda, "A 7-nm FinFET 1.2-TB/s/mm^2 3D-Stacked SRAM Module with 0.7-pJ/b Inductive Coupling Interface Using Over-SRAM Coil and Manchester-encoded Synchronous Transceiver," in IEEE Journal of Solid-State Circuits, vol. 58, no. 7, pp. 2075-2086, July 2023 vol. 58, no. 7, pp. 2075-2086, July 2023.

[3] A. Kosuge and T. Kuroda, "[Invited] Proximity Wireless Communication Technologies: An Overview and Design Guidelines," in IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 69, no. 11, pp. 4317-4330, Nov. 2022.