Beyond IC Advanced 3D Chip Integration and Low-power Circuit Design Technology for Next-generation AI Computing Systems

Kosuge Laboratory, Graduate School of Engineering The University of Tokyo

TOPICS

-

2025.6.3Researcher Prof. Amano presented his work titled “An SoC Design and Fabrication Hands-On Educational Course Within One Week Using Structured ASIC” at ISCAS 2025. Please check here.

-

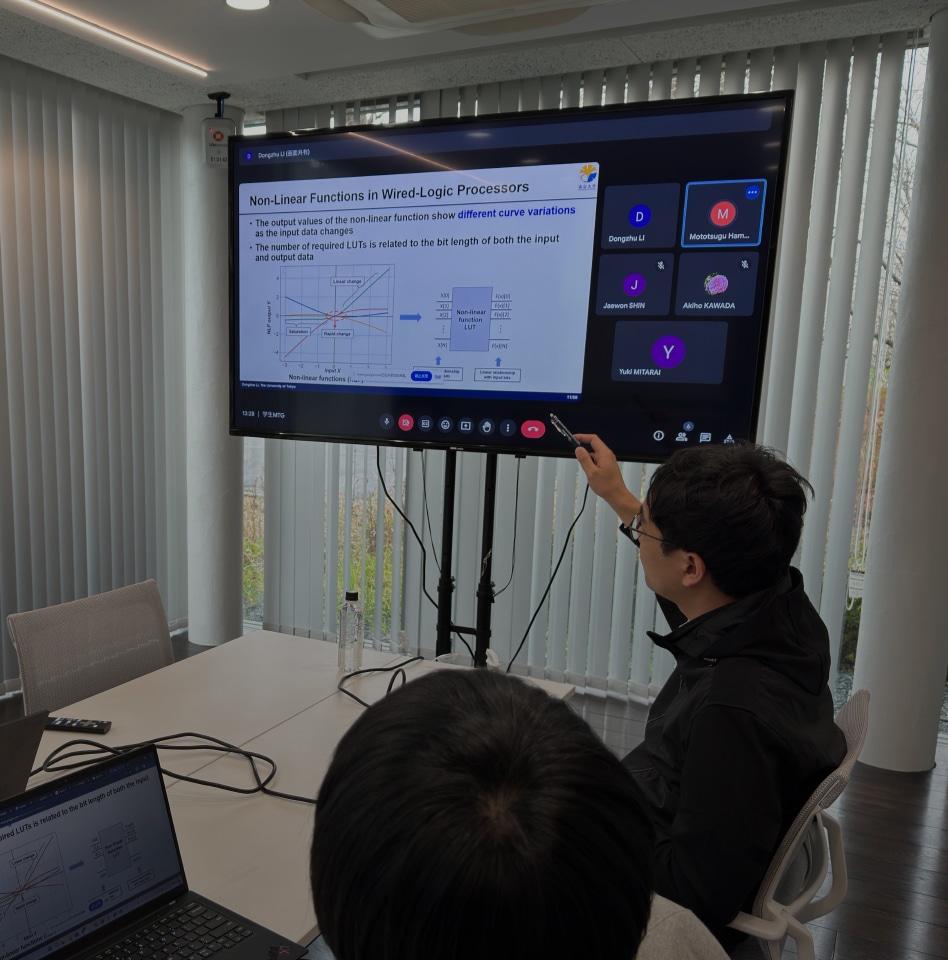

2025.6.3M2 Pan presented his work titled “An 83.7% Resource-Reduced Wired-Logic DNN Processor by Embedding Mixed-Precision Modules into Non-Linear Function LUTs” at ISCAS 2025. Please check here.

-

2025.6.3Dr. Kawano and D2 Huang presented their work at IEEE ECTC, which is the top internationa conference regarding 3D chip stacking and assembly. Here you can see the poster.

RESEARCH

THEME

AI technology is transforming and enriching our lives, but also consumes huge amount of power to process large amounts of data. To solve the power problem caused by AI, we need next-generation integrated circuits (Beyond IC) specialized for the AI era, with performance beyond what an extension of conventional ICs can offer. We are researching wired-logic processors and 3D integration technologies specialized for AI processing which will achieve power reductions of three orders of magnitude or more.

-

AI processor

With the new architecture and in/near memory computing techniques, we will achieve a 1,000 times improvement in power efficiency over conventional methods.

-

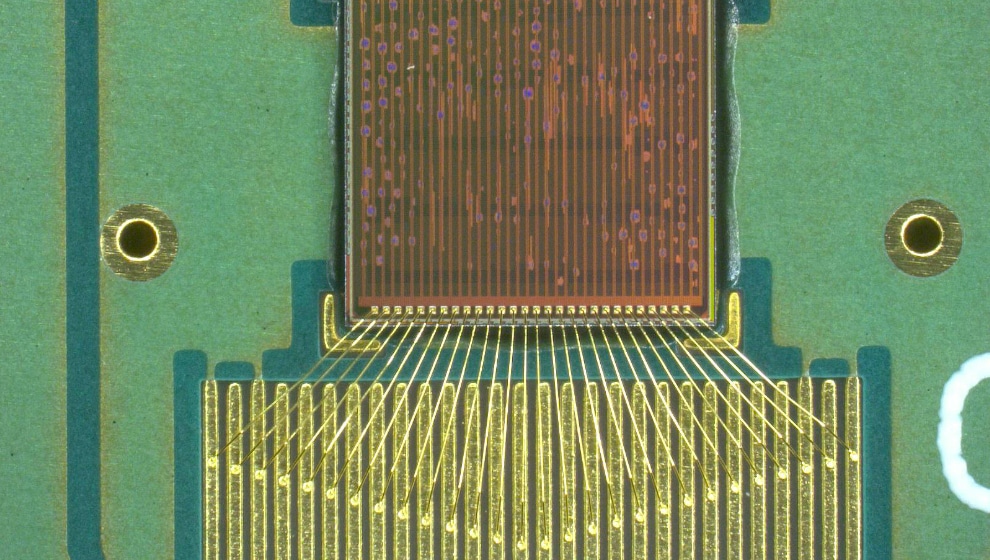

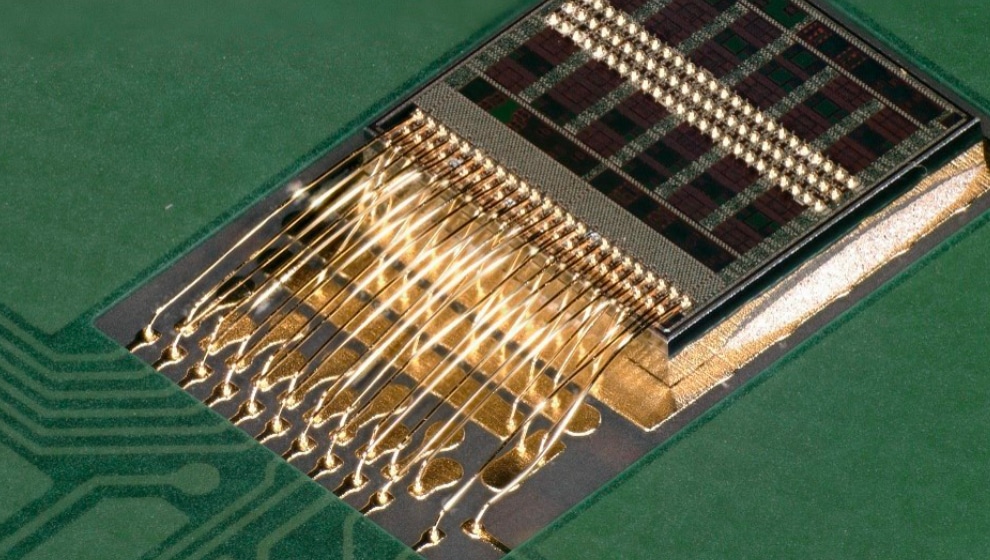

3D Chip Integration

We will develop a new chip stacking method for high-dense computing. Highly reliable and dense interconnection realize scalable and high throughput computing system.